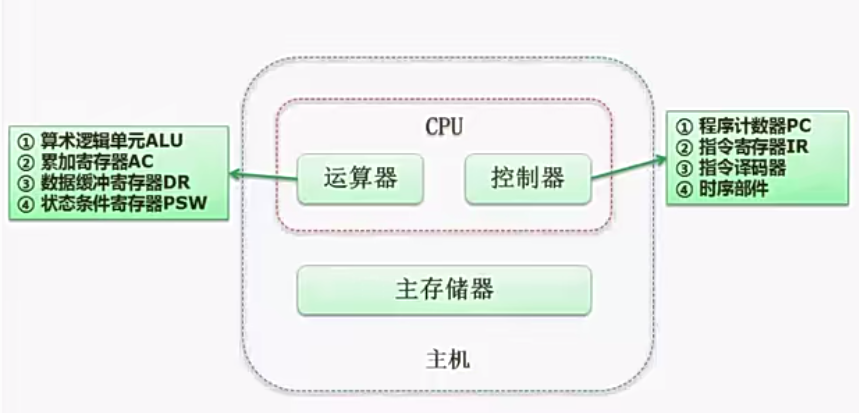

CPU 结构

CPU 组成:由运算器、控制器、寄存器组(读取速度最快)、内部总线组成

CPU 组成:由运算器、控制器、寄存器组(读取速度最快)、内部总线组成

运算器组成:

算数逻辑单元 ALU(Arithmetic logic unit):

实现对数据的算数和逻辑运算

累加寄存器 AC(Accumulator):

提供数据并暂存运算结果

数据缓冲寄存器 DR(Data Register):

作为 CPU 和内存、外设之间数据传送的中转站,暂时存放内存的指令或数据

状态条件寄存器 PSW(Program Status Word):

保存指令运行结果相关的标志位,如中断或进位等标志

控制器

指令寄存器 IR ( Instruction Register ) :

暂存当前 CPU 正在执行的指令【操作码和地址码在这里存储】对于用户是透明的

程序计数器 PC ( Program Counter ):

用于存放下一条指令的地址

地址寄存器 AR ( Address Register ):

保存当前 CPU 所访问的内存地址

指令译码器 ID ( Instruction Decoder):

分析指令操作码

计算机体系结构分类–Flynn

SISD 单片机

SISD 单片机

SIMD 并行,阵列处理(对数组操作)

MISD 理论模型

MIMD 个人 pc,计算机系统

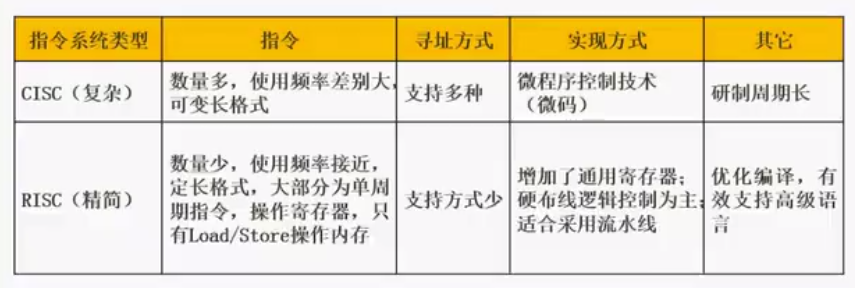

CISC 与 RISC

CISC 计算机不发达时期的产物,指令多,复杂

RISC 现代计算机,指令少,复杂度低,引入了寄存器,效率高

CISC 计算机不发达时期的产物,指令多,复杂

RISC 现代计算机,指令少,复杂度低,引入了寄存器,效率高

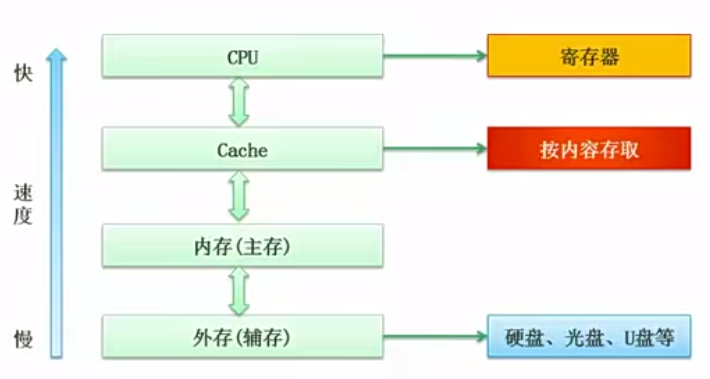

存储结构

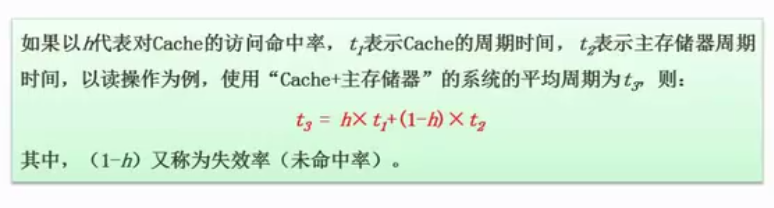

计算机层次存储结构

引入cache的原因:存在局部性原理 Cache 和 CPU 交互反交互的时候,暂停和内存的交互,速度就会很快。引入 cache 在提高速度的同时,也没有增加多少成本

引入cache的原因:存在局部性原理 Cache 和 CPU 交互反交互的时候,暂停和内存的交互,速度就会很快。引入 cache 在提高速度的同时,也没有增加多少成本

局部性原理

- 时间局部性:刚刚访问完数据又立即访问,不需要等待。

- 空间局部性:例如数组的初始化处理,在将数组初始化的过程中,初始化完这一个位置后立即去初始化下一个临近的空间。

- 工作集原理:工作即是进程,运行时被频繁访问的页面集合。将这些集合打包放进 Cache 里面去,就不需要频繁的替换掉。

主存储器

主存的分类

随机存取存储器: DRAM 动态 RAM,SRAM 静态 RAM(断电后无法写入保存数据)

只读存储器: MROM,PROM,EPROM,flash memory(断电后依然可以写入保存数据)

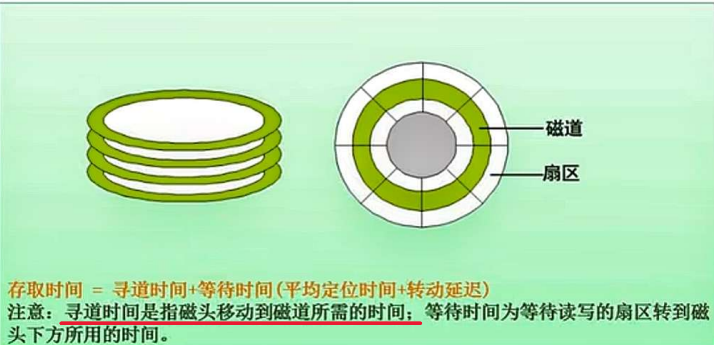

磁盘工作原理

总线系统

- 内部总线 通常是指微机内部的,外部芯片与处理器之间的联系,属于是芯片级别的总线

- 系统总线

属于是微机中各个插件板与系统之间的总线,属于是插件板级别的总线,如 PCI,VGA

- 数据总线:是用来传输数据的,比如说计算机的 32 位和 64 位,说明了系统总线的宽度就是这么个位数,那么一个周期能够传输的数据是 32164bit。

- 地址总线:若地址总线的位数是 32 位,那么它代表的地址总线宽度为 2^32,即 4G。因此操作系统是 32 位的,那么他能管理的内存最多是 4g,当然也有硬件有一定关系。

- 控制总线: 发送相应的控制信号的总线。

- 外部总线 属于是外部设备的总线。